开源综合工具Yosys中的Verilog Parser

我之前分析了开源仿真工具Icarus Verilog中的verilog parser,恰巧最近又看了综合工具Yosys中的Verilog Parser,就写几句话记录一下。

Yosys介绍

根据官网www.cliford.at/yosys描述:

Yosys is a framework for Verilog RTL synthesis. It currently has extensive Verilog-2005 support.

就是支持Verilog2005的综合框架。为什么说是框架?因为Yosys除了提供综合网表外,还提供了综合方法和流程、基本的综合算法、逻辑等价性检查等功能(就是开源代码本身)。

Yosys的功能主要有以下几点:

- 支持几乎所有的Verilog2005中的可综合语法

- 把Verilog转换成BLIT/EDIF/BTOR/SMT-LIB/Simple RTL Verilog等

- 内建逻辑等价性检查

- 映射到ASIC标准单元库

- 映射到Xilinx 7系列和Lattice iCE40 FPGA

- 是客户定制化流程的基础和前端

可以扩展C++代码来增加自己的综合优化算法。

Yosys中的Verilog Parser

之前提到Icarus Verilog的编译过程:

经过gpref、flex、bison处理后,parse.cc的源文件就有了。实际上compile的过程主要就是调用parser的过程。

那Yosys是怎样的呢?我们知道,要综合必须要先读入Verilog源代码,那么我们就去看看Yosys的源码:https://github.com/YosysHQ/yosys。

在frontends/verilog目录,我们找到了Verilog Parser源码。

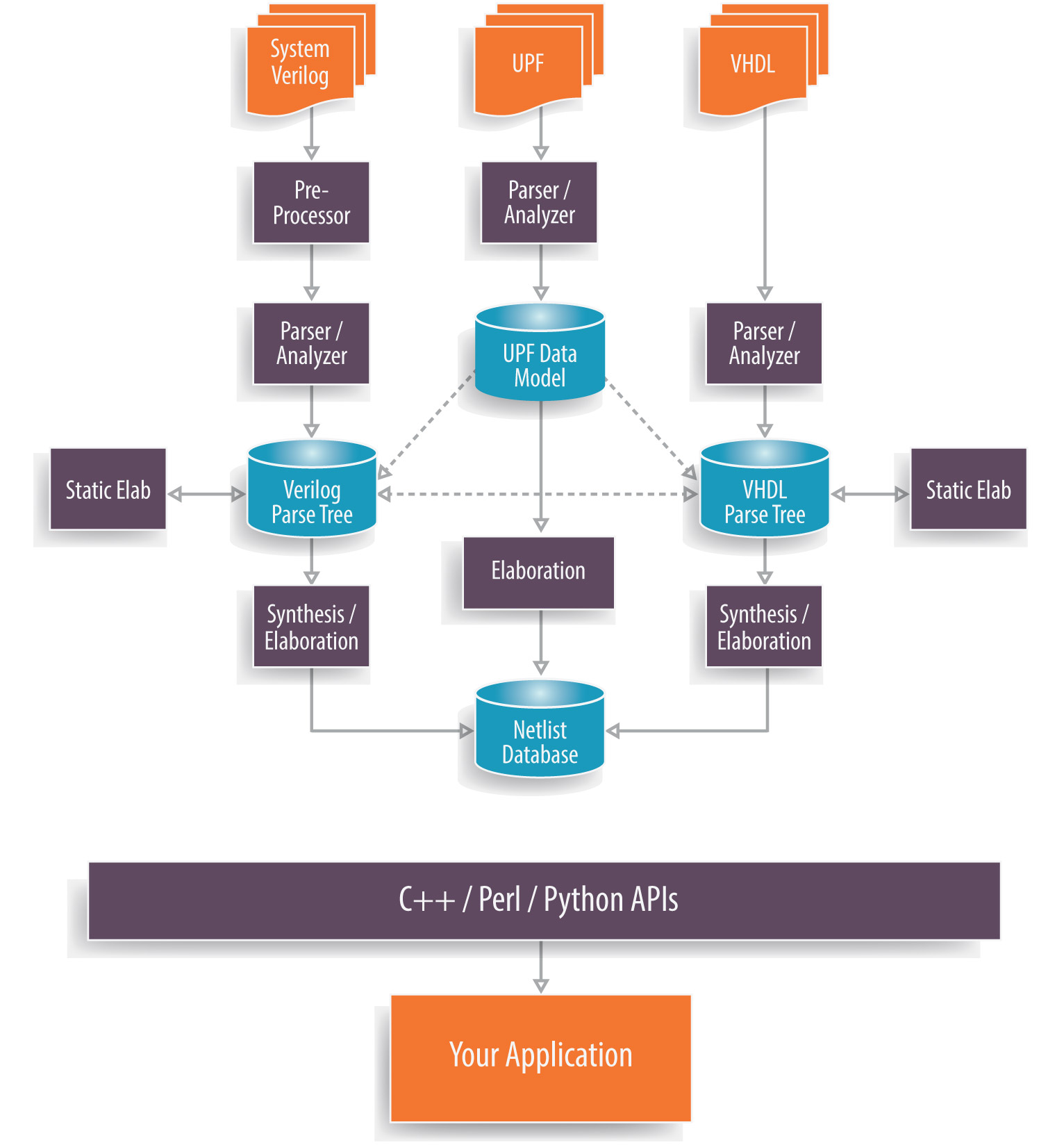

插入一段题外话:顺便提一下在frontends目录下还有其它语言或库的parser,如aiger、blif、ilang、json、liberty、verific。其中verific是一个公司名,全名Verific Design Automation,专门提供SystemVerilog、VHDL、UPF Parser,感兴趣可以深入了解下:https://www.verific.com。Verific的产品如下图:

回到今天的主题上来,看一下frontends/verilog目录:

有了学习Icarus的基础,从文件名上也可以看出大概了。

- preproc.cc 预处理

- verilog_lexer.l flex输入文件

- verilog_parser.y bison输入文件

- verilog_frontend.cc/h 根据parse的结果创建AST

- const2ast.cc bison后调用const2ast存到AST节点里。

- Makefile.inc 编译脚本

注:AST是抽象语法树(Abstruct syntax tree)。

可以看到与Icarus过程基本一样,先后调用预处理、flex、bison,最终建立AST。

对于学习而言,建议可以深入看看预处理的实现,一段单纯文本操作的C++代码。另外,可以深入研究AST的数据结构的定义,详见yosys/frontends/ast/ast.h,但这不属于parser的话题,我们可以后面再另外讨论。